DRAM 관련 용어

■Array

실제 data 가 저장되는 cell 이 배열된 물리적인 구조를 나타내며 이 배열은 열과 행으로 구성되어 있음

■Bank

메모리를 논리적으로 나눈 단위를 bank 라고 함

bank 내의 data 는 한번에 access 할 수 있으며 각 bank 는 독립적으로 동작함

Word line 은 row address 를 가짐

Sense amp 가 연결되는 bit line 은 column address 를 가짐

<Bank 구조>

■Page

Word line 에 연결된 FET 의 bit 수를 나타냄 보통 1KB or 2KB 의 크기를 가짐

Page size 는 한번에 켜져야 하는 sense amp 의 수를 나타내는데

Page size 가 작을수록 보다 적은 수의 sense amp 만 동작시켜도 되기 때문에 전력소모를 줄이는데 유리함

Page size=(2^(column address bits)∗I/O(DQ)bits) / 8 [Byte]

Ex) column address 가 10bit 이면 row 당 1K 의 bit line 이 있고 DQ bit 가 x8 이면 page size 는 (1K*8)/8=1KB 가 됨

→ Page size / bank size 계산 예

Bank group 수 : 4개

Bank group 에 속하는 bank 의 수 : 4개

Word line 에 연결된 bit 수=2^10=1024=1Kb

Page size=1024*4(data bus width) / 8=512Byte

이런 page 가 1bank 당 0~16 17개(row address bits 0~16)가 있음

Bank size : 512*17=8704Byte

■Data bus width

한번의 access 로 처리할 수 있는 data 량을 의미함

X4, x8, x16 등으로 나타내며 Data bus width 가 넓을수록 한번의 access 로 더 많은 data 를 전송할 수 있음

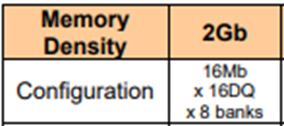

■Density

DDR 의 chip 은 여러개의 die 로 이루어져 있는데 die 하나의 저장 용량을 나타냄

16Mb : array 하나에 저장할 수 있는 bit 수

16DQ : data bus width x16

8banks : bank 수 8개

→16Mb*16*8=2Gb

■Bank group : bank 들을 묶은 group. bank group 은 여러 bank 를 묶어서 동시에 access 할 수 있음

Bank group 을 사용하면 여러 bank 간에 동시에 data 를 access 할 수 있기 때문에 memory access 의 효율성을 높일 수 있음

But bank group 이 많아질수록 전력 소모가 커짐

■Rank

Memory chip 의 물리적인 그룹을 나타냄 각 rank 는 병렬 access 가 가능함

내부적으로는 독립된 구조이지만 memory controller 와 data 를 주고 받는데에 있어 하나의 채널을 공유하는 구조

■Channel

메모리 controller 와 memory 간의 물리적 연결을 나타냄 각 channel 은 완전히 독립적인 data bus 를 가지고 있기 때문에 동시에 서로 다른 data 를 보낼 수 있음

Channel 을 사용하면 병렬로 data 를 전송하여 대역폭을 향상시킬 수 있음

'Electronic' 카테고리의 다른 글

| TVS 란? Varistor 란? Datasheet spec 확인, TVS vs Varistor 비교 (0) | 2024.12.18 |

|---|---|

| MOSFET 이란? MOSFET 동작 영역, Symbol, Datasheet spec 확인 (0) | 2024.12.18 |

| DRAM 이란? LPDDR5 bank 구조, 추가 기능-WCK, DVFS (0) | 2024.12.18 |

| DRAM이란?DRAM동작 (4) | 2024.03.22 |

| DRAM이란?DRAM구성,cell 구조 (0) | 2024.03.20 |