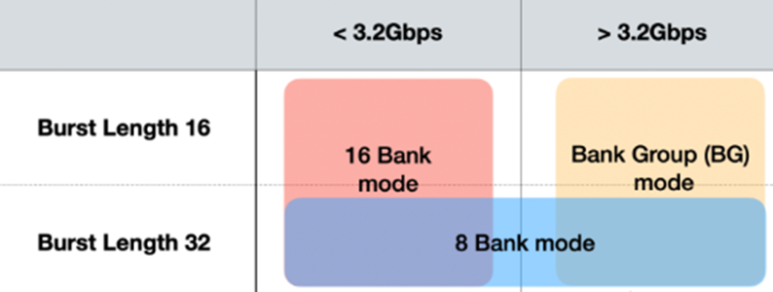

LPDDR5■ Bank OperationsLPDDR5 는 3가지의 Bank 구조를 가짐1) 8B mode-8개의 bank, bank group 없음-Full frequency range2) BG mode-4개의 bank group, bank group 당 4개의 bank-High data rate support(WCK>1.6GHz)3) 16B mode-16개의 bank, bank group 없음-Low data rate support(WCK≤1.6GHz) ■ WCKLPDDR5 는 IO clock 이 빨라지면서 data strobe 와 data 사이의 timing 을 맞추는 것이 어려워짐이에 따라 command/address 를 위한 clock(CK) 와 data 전송을 위한 clock(WCK) 가 분..