DRAM 동작

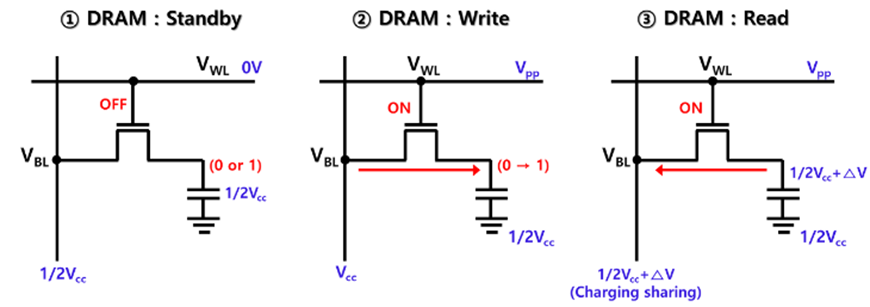

Write, read 동작 시 word line 에 bias 를 인가하여 transistor 를 on 상태로 만들어줌(Active command)

■ Write

Bit line 에 VDD를 인가하면 전자가 TR 에 주입되어 capacitor 에 charge 되면서 1의 정보를 저장함

반대로 0V 를 인가하면 capacitor 의 전하는 discharge 되면서 0의 정보가 저장됨

WL=high, BL=high : capacitor charge, data 1 write

WL=high, BL=low : capacitor discharge, data 0 write

■ Read

Bit line 에 ½*VDD 를 인가(pre-charge)하여 bit line 의 전위차의 변화를 sense amplifier 로 비교 및 증폭하여 data 가 0인지 1인지 판단함

전위차가 증가하면 1, 감소하면 0 의 data 를 read 함

WL=high, BL=1/2*VDD 일 때 BL 이 1/2*VDD 보다 증가 : data 1 read

WL=high, BL=1/2*VDD 일 때 BL 이 1/2*VDD 보다 감소 : data 0 read

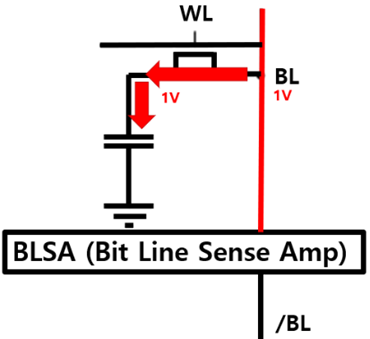

■ Refresh

Capacitor 특성상 저장된 전하는 금방 방전되기 때문에 주기적으로 전하를 채워주는 refresh 과정을 반복하여 data 값을 유지시켜주는 것

Refresh 과정 :

1) 특정 주기에 따라 bank 내의 word line 중 하나가 선택됨

2) word line 에 달린 TR gate 에 VDD 전압이 걸리면서 capacitor 와 bit line 간 전자가 이동할 수 있게 됨

3) 방전된 capacitor 와 bit line 사이에 charge sharing 이 발생함

4) Sense amp 에서 ½*VDD 인 bit line 과 비교 후 1(VDD)로 증폭

5) 증폭된 전자는 capacitor 에 재 충전됨

* Refresh 동작에 의해 추가적인 전력이 소모되고 refresh 동안 같은 word line 에 연결된 cell 들이

다른 동작을 수행할 수 없는 공백기가 생기는 문제가 발생함

; refresh 주기는 길수록 좋음(자주 일어나지 않을 수록 좋음)

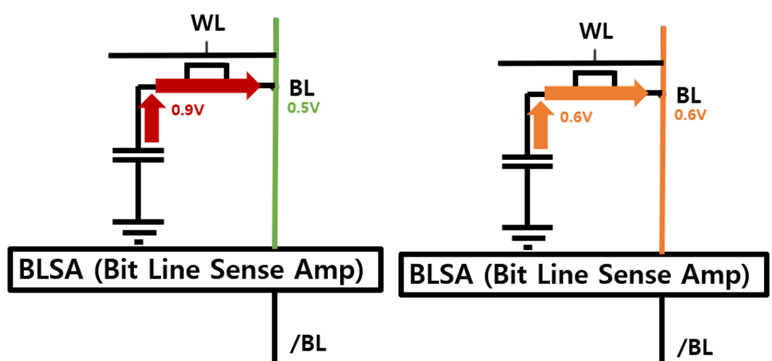

■ Sense amplifier

Reading 과정에서 bit line 의 전압 변화를 감지하는 역할을 하며 reading 으로 인해 손상된 data 를 refresh 하는 역할도 함

Bit line 은 ½*VDD 으로 고정된 전압을 가지기 때문에 이 전압 보다 크면(1/2*VDD+∆V) 1, 작으면(1/2*VDD-∆V) 0으로 만들어주는 역할을 함

■ Pre-charge

Data 를 read 하기 전 bit line 에 ½*VDD 를 인가하여 capacitor 의 전하 상태를 미리 파악하는 과정

■ Pre-fetch

Memory access 속도를 향상시키기 위해 Memory controller 가 data 를 요청하기 전에 미리 data 를 메모리로 가져오는 과정

다음 access 에 필요한 data 를 미리 load 하여 access delay 를 최소화할 수 있음

Memory 가 작동할 때 한 bit 씩 읽어 들이는 대신 4개, 8개의 cell 을 동시에 작동시켜 4bit(4n), 8bit(8n) 씩 한번에 읽어들이는 방식

■ ODT(On Die Termination)

DRAM 내부 termination 저항을 변경하여 여러개의 DRAM 간의 신호 반사를 예방함

Read 나 write 동작 동안 안쓰는 메모리 모듈은 low impedance, access 중인 모듈은 high impedance 로 유지해야 반송파를 만들지 않아 SI 측면에서 유리함

■ ZQ Calibration

SOC(controller) 와 DRAM 간의 impedance mismatch 를 감소시키기 위해 impedance 를 보정하는 것

신호 반사와 impedance 불연속을 줄여 시스템 안정에 기여함 외부에 reference 저항 240ohm 을 연결해주어야 함

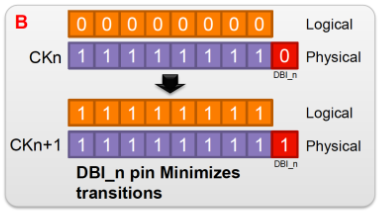

■ DBI(Data Bus Inversion)

Data bus 의 전력소모를 줄이고 신호 noise 를 감소시키는데 사용됨

Low(0) or High(1) 의 개수에 따라 전력을 덜 쓸 수 있도록 data 를 전송하기 전에 bit 를 inversion 시켜서 보냄

■ DBI(Data Bus Inversion)

Data bus 의 전력소모를 줄이고 신호 noise 를 감소시키는데 사용됨

Low(0) or High(1) 의 개수에 따라 전력을 덜 쓸 수 있도록 data 를 전송하기 전에 bit 를 inversion 시켜서 보냄

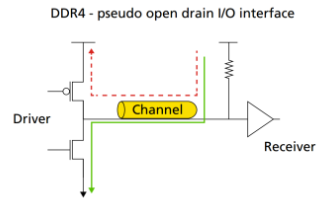

반면 DDR4 의 경우 termination 저항이 VDD 에만 연결되어 있기 때문에 driver 가 0을 전송할 때는 전류가 흐르지만(초록색) 1을 전송할 때는 전류가 흐르지 않음(빨간점선)

DBI 는 1을 전송할 때 전력소모가 작은 성질을 이용하여 8bit data 마다 DBI 사용 여부를 나타내는 DBI_n pin 을 하나 더 두고 8bit data 상 0의 개수가 1의 개수보다 더 많을 경우 0과 1을 뒤집어 보내고 DBI_n=0 으로 표시함

■ DM(Data Mask)

Data 가 Read 되거나 write 될 때 각 data bit 와 함께 data mask bit 도 함께 전송됨

이 data mask 신호는 해당 data bit 가 유효한지 여부를 나타냄

Data mask 를 사용하면 data 전송 중에 발생할 수 있는 오류를 식별하고 처리하여 시스템의 안정성을 향상시킬 수 있음

'Electronic' 카테고리의 다른 글

| TVS 란? Varistor 란? Datasheet spec 확인, TVS vs Varistor 비교 (0) | 2024.12.18 |

|---|---|

| MOSFET 이란? MOSFET 동작 영역, Symbol, Datasheet spec 확인 (0) | 2024.12.18 |

| DRAM 이란? LPDDR5 bank 구조, 추가 기능-WCK, DVFS (0) | 2024.12.18 |

| DRAM이란?DRAM관련 용어 (1) | 2024.03.25 |

| DRAM이란?DRAM구성,cell 구조 (0) | 2024.03.20 |