MOSFET

■MOSFET 이란?

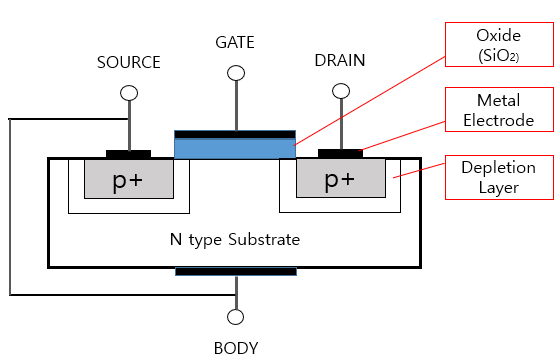

MOSFET(Metal Oxide Semiconductor Field Effect Transistor) 은

MOS구조(Metal-Oxide-Semiconductor)를 통해 전계를 생성하여 동작하는 트랜지스터를 말함

MOS 구조

MOS 구조는 Gate 에 존재하며 Drain&Souce 에 어떤 반도체 종류를 사용하느냐에 따라

N-MOSFET(Drain, Source : N dopping)

P-MOSFET(Drain, Source : P dopping) 으로 나눌 수 있음

N-MOSFET 구조

P-MOSFET 구조

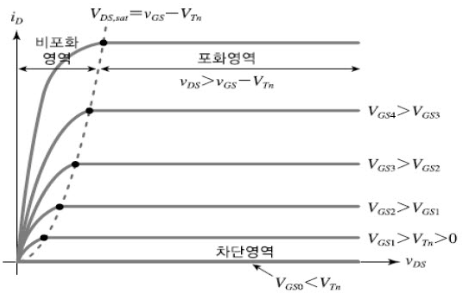

■ MOSFET 동작 영역

<N-MOSFET 기준>

1) cut off 영역

-디지털 논리 소자에서 off switch 처럼 동작

-전압조건: Vgs < Vth (Vds 는 영향 없음) ; threshold 전압 보다 gate 전압이 낮음

-전류 흐름 : drain source 간에 전류 흐름 없음(차단 상태), id=0

2) triode 영역(linear 영역)

-디지털 논리 소자에서 on switch 처럼 동작 ; 이 때 선형 저항 소자처럼 동작하게 됨

-전압조건: Vgs > Vth & 0 < Vds < Vgs-Vth

-전류 흐름 : drain source 간에 전류 흐름 있음(도통 상태, Vgs전압에 선형 비례)

3) saturation 영역(포화영역)

-증폭기 역할이 가능한 영역 ; 디지털 논리소자로써 용도 없음

-전압조건: Vgs > Vth & Vds > Vgs-Vth

-전류 흐름 : drain source 간에 전류 흐름 있음(도통 상태, 더 이상의 증가 없이 포화됨)

* pinch off

N-MOS pinch off

P-MOS pinch off

Vgs > Vth 일 떼 Vds 전압이 증가하면 id(drain 전류)가 증가하게 되는데

Vds=Vgs-Vth 가 되면 전류는 더 이상 증가하지 않고 일정한 값을 유지하게 됨

이 전압을 pinch off 전압이라고 함

gate 전압에 의해 형성된 채널이 Vds 에 의해 채널의 출구가 닫히도록하는 전압을 말함

채널의 출구가 닫힘으로써 전류가 일정해짐

saturation 영역에서 전류는 Vgs 전압에 의해서만 조절됨

Vgs < Vth : off 상태

Vgs > Vth : on 상태

ex) P-MOS 에서 Vth=-1.5V 일 때(보통 N mos 를 기준으로 언급하기 때문에 -가 붙음)

gate 전압이 12V, source 전압이 3V 이면 Vgs 는 -9V 가 됨

이때 Vgs<Vth 이므로 turn on 될 수 없음

<P-MOS 동작조건>

N-MOS 와 반대로 Vsg > Vth 여야 turn on 된다고 볼 수 있음

Vsg < Vth : off 상태

Vsg > Vth : on 상태

Vsg > Vth & Vsd < Vsg-Vth : triode 상태

Vsg > Vth & Vsd > Vsg-Vth : saturation 상태

■ MOSFET Symbol

MOSFET 의 symbol 에서 화살표는 전자의 이동방향을 나타냄

(BJT symbol 에서 화살표는 전류의 방향을 나타냄)

N-MOSFET에서 전자는 source 에서 들어오고

P-MOSFET 은 source 로 나가게 됨

■ MOSFET Datasheet spec 확인

-Vds : FET 가 off 된 상태에서 FET 의 drain 단과 source 단을 측정할 경우

이 값이 60V 가 넘으면 FET 가 손상을 입음

-Vgs : FET 를 on/off switching 용으로 제어하기 위해 gate 단에 입력해야 하는 전압의 안정적인 범위

보통 FET 를 on 시키는 조건에서 15~18V 사이로 gate 단의 제어 전압 레벨을 정함

-Id : FET 에 흐르는 부하전류로 FET 의 부하가 이 값의 50% 이하가 되도록 하기

-Ptot : FET 가 on 상태일 때 소비할 수 있는 최대 전력으로

Ptot > Id^2∗Rds(on) 을 만족 시켜줘야함

-Rds(on) 은 FET 가 on 상태일 때 FET 자체가 갖는 작은 저항 값으로 이 저항에서 발열이 발생하게 됨

이 발열량이 Ptot 값을 넘지 않도록해야함

-Tj : FET 의 최대 junction 온도로 junction 온도는 Rthj-a 값을 통해

Tj=Ta+Rthj-a*Ptot 의 식으로 부터 구할 수 있음

이렇게 구한 값이 150℃ 보다 작아야 함

-V(BR)dss : drain-source 에 해당 전압이상의 전압이 걸리면

breakdown 이 발생하여 avalanche 항복이 발생하게 됨

avalanche 항복 시 FET 내부 diode 에 대해 역방향으로 흐르는 전류를 avalance 전류 Ias 라고 함

FET 가 breakdown 되면 Ias*V(BR)dss 의 전력 손실이 발생하게 됨

-Idss : FET 가 off 된 상태임에도 불구하고 FET 의 물리적인 반도체 구조에 의해서 drain-source 로 누설되는 전류로 작을수록 좋음

-Igss : FET가 on 상태일 때 Gate 의 제어 신호가 FET 의 body 로 누설되는 전류를 의미함 작을수록 좋음

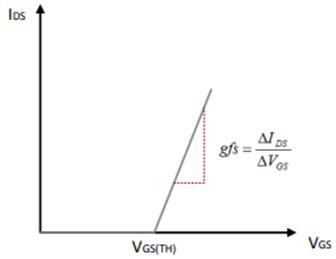

-Vgs(th) : FET 를 on 시키기 위한 gate 단에 인가해야 하는 최소한의 전압=threshold 전압

-gfs : forward transcouductance

gate-source 간의 전압 변화량에 대한 drain 전류의 변화량을 의미함

(saturation 영역에서는 gate 전압에 따라 전류 값이 바뀜)

-td(on) : turn on delay time

Vgs 전압이 10% 까지 rising 하고 Vds 전압이 90% 까지 falling 할 때 까지 걸리는 시간

-tr : rise time

Vds 전압이 90%에서 10% 로 falling 할 때 걸리는 시간으로 Id 가 rising 하기 시작하며 turn on loss 는 해당 시간에 대부분 존재함

-td(off) : turn off delay time

Vds 전압이 10% 까지 rising 하고 Vgs 전압이 90% 까지 falling 할 때 까지 걸리는 시간

-tf : fall time

Vds 전압이 10%에서 90% 로 rising 할 때 걸리는 시간으로 Id 가 falling 하기 시작하며 turn off loss 는 해당 시간에 대부분 존재함

'Electronic' 카테고리의 다른 글

| Bead 란? 기능, 역할, 등가회로, Inductor 와의 차이점, datasheet spec, 정격전류, DCR, 임피던스 (0) | 2024.12.18 |

|---|---|

| TVS 란? Varistor 란? Datasheet spec 확인, TVS vs Varistor 비교 (0) | 2024.12.18 |

| DRAM 이란? LPDDR5 bank 구조, 추가 기능-WCK, DVFS (0) | 2024.12.18 |

| DRAM이란?DRAM관련 용어 (1) | 2024.03.25 |

| DRAM이란?DRAM동작 (4) | 2024.03.22 |