LPDDR5

■ Bank Operations

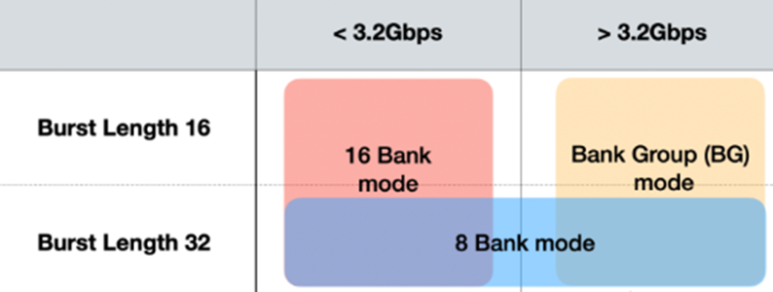

LPDDR5 는 3가지의 Bank 구조를 가짐

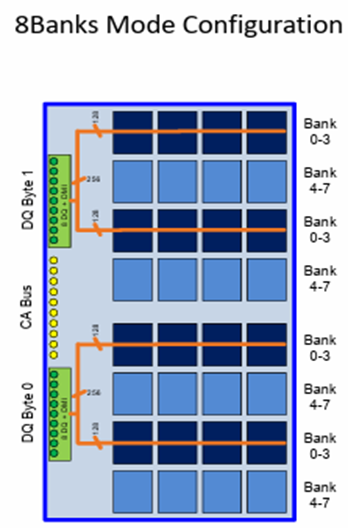

1) 8B mode

-8개의 bank, bank group 없음

-Full frequency range

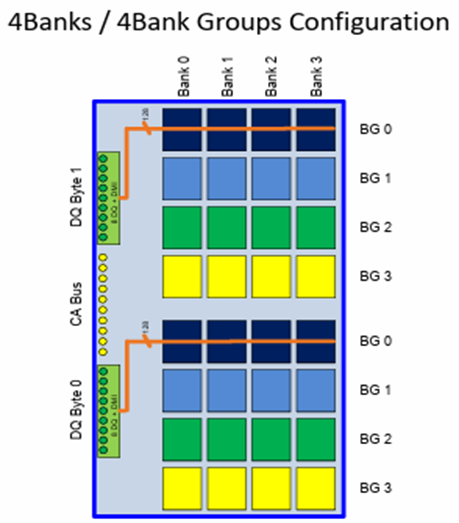

2) BG mode

-4개의 bank group, bank group 당 4개의 bank

-High data rate support(WCK>1.6GHz)

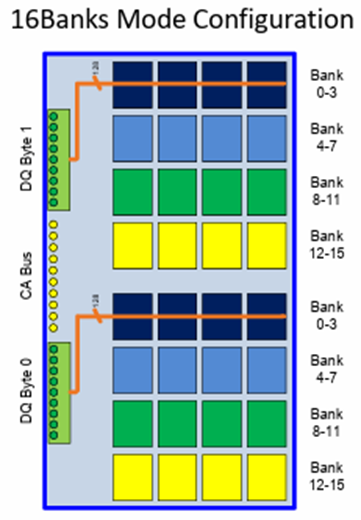

3) 16B mode

-16개의 bank, bank group 없음

-Low data rate support(WCK≤1.6GHz)

■ WCK

LPDDR5 는 IO clock 이 빨라지면서 data strobe 와 data 사이의 timing 을 맞추는 것이 어려워짐

이에 따라 command/address 를 위한 clock(CK) 와 data 전송을 위한 clock(WCK) 가 분리됨

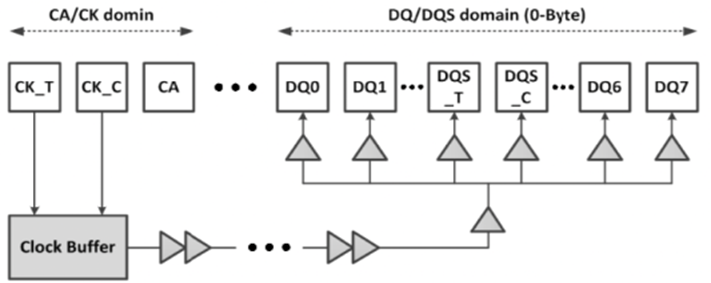

LPDDR4x clock 구조

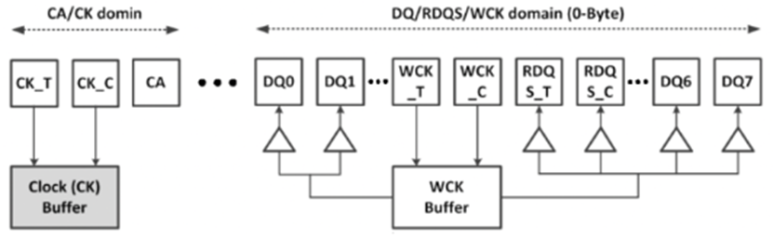

LPDDR5 clock 구조

CK 와 WCK 를 분리하면 DRAM 회로 내에서 strobe 를 만들기 위한 clock path 가 짧아져 jitter 특성확보에 유리해짐

LPDDR4 clock 구조에서는 DQS 를 만들기 위한 clock 이 clock buffer 를 거친 후 여러 개의 buffer 를 거치게 되어 jitter 특성이 나빠지지만

LPDDR5 clock 구조에서는 별도의 WCK buffer 를 통해 clock 을 공급 받은 뒤 훨씬 적은 수의 buffer 를 거치기 때문에 clock jitter 의 영향이 적어지고 clock 속도를 올리기 유리해짐

■ DVFS(Dynamic Voltage Frequency Scaling)

LPDDR5 는 power 소모를 줄이기 위해 2가지 종류의 DVFS 를 지원함

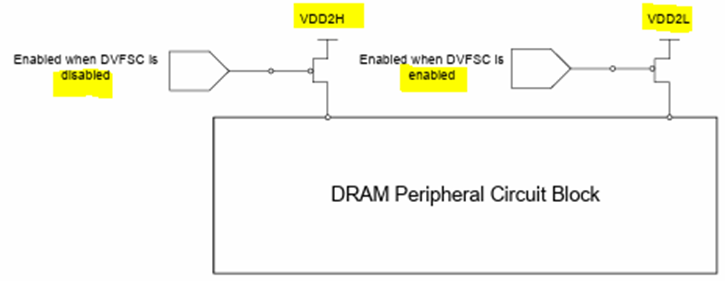

1) DRAM 내부 power 감소 : DVFSC(DVFS core)

미리 1.05V(VDD2H) 와 0.9V(VDD2L) 를 공급한 상태에서 스위칭하여 전원 사용

DVFSC enable 설정 시 VDD2L 전원 사용, disable 설정 시 VDD2H 전원 사용

MR19 OP[1:0] 로 DVFSC enable/disable control 가능

DVFSC 는 WCK=800MHz 까지 지원 가능

2) interface power 감소 : DVFSQ(DVFS VDDQ)

0.5V 와 0.3V 를 공급받는 상태에서 스위칭 하는 것이 아닌 단일 VDDQ 전원이 0.5V 와 0.3V 로 변함

DVFSQ enable 설정 시 VDDQ=0.3V, disable 설정 시 VDDQ=0.5V

MR19 OP[3:2] 로 DVFSQ enable/disable control 가능

VDDQ ramp up/down 동안 LPDDR5 는 DVFSQ enable 상태로 동작함

'Electronic' 카테고리의 다른 글

| TVS 란? Varistor 란? Datasheet spec 확인, TVS vs Varistor 비교 (0) | 2024.12.18 |

|---|---|

| MOSFET 이란? MOSFET 동작 영역, Symbol, Datasheet spec 확인 (0) | 2024.12.18 |

| DRAM이란?DRAM관련 용어 (1) | 2024.03.25 |

| DRAM이란?DRAM동작 (4) | 2024.03.22 |

| DRAM이란?DRAM구성,cell 구조 (0) | 2024.03.20 |